接下来,我们来聊聊英特尔在芯片封装技术方面的一些最新动向。

大家有关注过最近这几年CPU市场的技术动向就会发现,现如今无论英特尔、还是AMD,其实都没有再去研发“一整块”的大号CPU产品。大家做的都是模块化设计,之后再通过先进封装技术将其整合起来,形成“一颗”完整的解决方案。

模块化的设计有很多好处,比如可以降低CPU迭代的成本,允许CPU在更新换代时只更换其中的部分模组,同时沿用不那么重要的部分。同时,模块化设计也大幅简化了超多核CPU的构成方式,允许厂商大量复用“小核心”来组成一颗大尺寸的多核CPU,而不太需要考虑原生超多核布局所带来的走线困难。

但是,模块化设计也有局限性。比如在AMD的CPU上可以看到,他们是将多个小尺寸的计算核心和IO核心分开来布局在PCB上,以此所构成的超多核方案。这种设计的最大问题,就是跨模组之间过长的走线路径会造成极其明显的通讯延迟问题。以至于哪怕是在家用级的锐龙9处理器上,玩家们也往往不得不手动锁定(游戏)线程在一颗模组内部,才能避免跨模组通信带来的显著性能降低。而且过于分散的模组互联布局还会带来隐性的功耗短板,从而降低CPU的整体能效。特别是对于企业级的超多核CPU服务器来说, 由于CPU跨模组通信所带来的额外功耗浪费,有时候便不能被忽视。

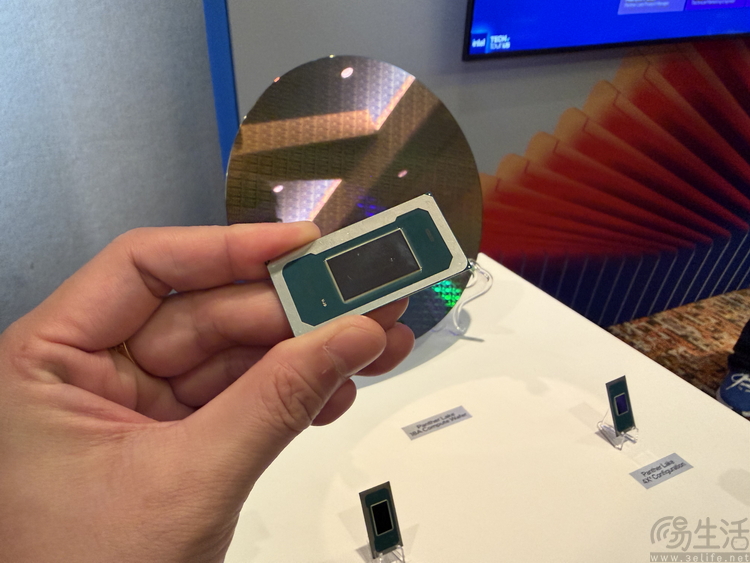

正因如此,英特尔从很早就开始有意避免这种“简单粗暴”的多核模组设计方案。取而代之的,是他们开发出了自家的Foveros系列多芯片互联封装设计。

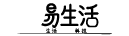

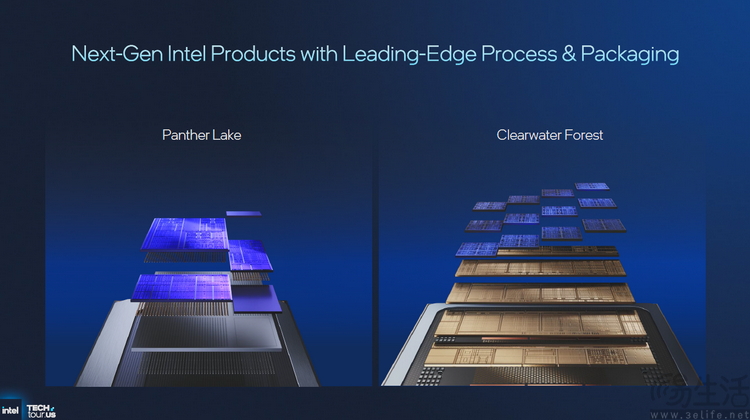

以英特尔下一代消费级CPU使用的Foveros-S 2.5D技术为例,它就是将多个小尺寸的芯片(Die)置于无源互联层(Passive Base Die)之上,通过互联层内部的走线来完成多核心互联通信。

与传统的、基于PCB内部走线的互联方案相比,Foveros-S 2.5D封装的焊点密度提高了16倍之多,同时单bit的通信功耗从0.5pJ(皮焦耳)降低到仅0.15pJ。

当然,这还没完,针对企业级的更大型处理器设计,英特尔还有更进一步的Foveros Direct 3D互联。它的焊点密度更是可以达到传统PCB上BGA焊接工艺的100倍之多,单bit传输功耗低至0.05pJ,只有PCB多芯片互联工艺1/10的功耗。

而且Foveros Direct 3D封装所使用的有源基板(Active Base Tile)并不只担当“互联层”的作用,它还可以在内部集成内存控制器、甚至是内含巨大的LLC(Last Level Cache)缓存。有没有觉得有点眼熟?其实这就是传闻中的英特尔版本“X3D”方案。只不过这个“X3D”同时具备了缓存、内存控制器、CPU核心互联层的功用,可以说在客观上就彰显了英特尔在复杂封装工艺上的大胆设计思路。